2003. 8.19 Ver1.0 Final公開

2003. 5. 6 Beta版更新、リトライバグ修正、リセット/ウェイトオプション追加

2003. 4.30 Beta版公開

2003. 4.25 再開

2002.11.21 新規

カメレオンUSBベースによる開発は終了しました。

不安定なシステムのデバッグに根気強くつき合って下さったシーエー寺脇様に、厚く御礼申し上げます。

今後はEZ-FPGA版PROMエミュレータに引き継がれます。

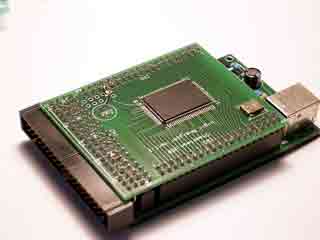

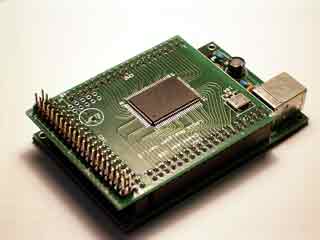

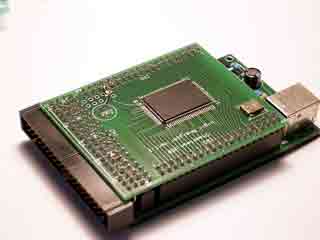

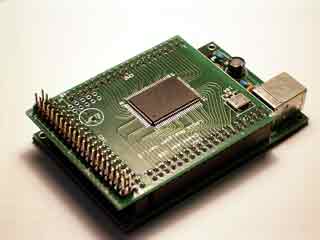

カメレオンUSB+ロジアナ基板を使って、ROMエミュレータにしてしまうものです。

カメレオンUSBをしらない人は、こちらからどうぞ

特徴

・カメレオンUSB+ロジアナ基板をそのまま流用

・64Kbit~4MBitまでの一般的なDIP28/DIP32ピンのROMに対応

・一部のFlashROMにも対応、ただしの通常リード機能のみ

・5.0V TTLレベルの他、3.3V LVCMOSレベルにも適合

・USBによる高速ダウンロード

・特定アドレスのアクセスを検出できるアクセストリガ機能

・ダウンロード中にターゲットのRESET信号を制御可能

・Win32コンソールプログラム

・エミュレーション動作中のリアルタイムダウンロード不可

・単体バックアップ機能無し

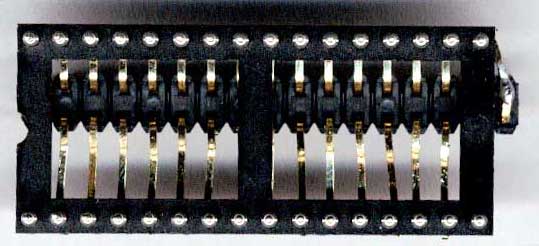

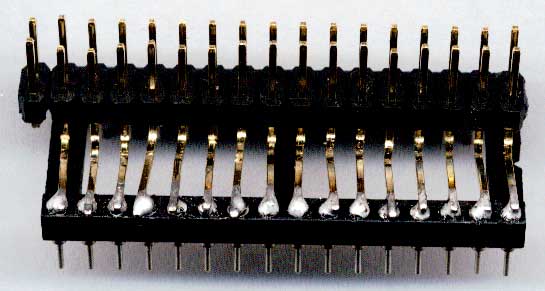

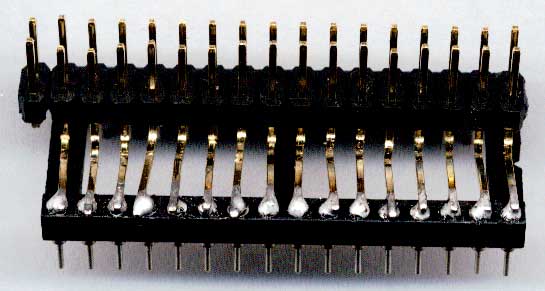

・表裏2パターンのコネクタに対応

表だし  裏だし

裏だし

Download

注意事項!

著者は、本システムの使用に関するいかなる保証もいたしません。

保護回路等の設計を盛り込み、特定条件での動作確認は行っておりますが、不具合が発生する可能性は十分にあります。 したり、最悪のケースでは本システムやターゲットシステムを破壊してしまう可能性も考えられます。

本システムの使用に関するすべての問題と責任は、各自使用者が負う必要があります。

DIP28/32用プローブ回路図

Ver1.00 CPLD/ホストプログラム、ソース一式

※回路図とCPLDデザインファイルはプローブコネクタの表だし、裏だしの2種類が存在します。ホストプログラムは共通です。

DIP28/DIP32対応PROMプローブの制作方法(例)

0.回路図を良く確認します。

回路、部品構成、大きさ、製作順番などを頭のなかでしっかり組み立てます。

特に、プローブ部分は小さくまとめないと、ターゲットの部品と干渉を起こすことがあります。

コネクタの表だしと裏だしではコネクタピン配置が異なりますが、プローブ回路は同じです。

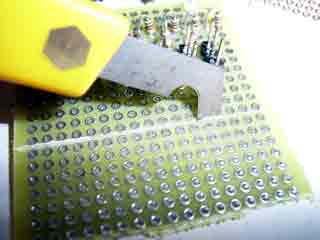

1.32ピンのヘッダーピンを、適当にカットした基板に取り付けます。

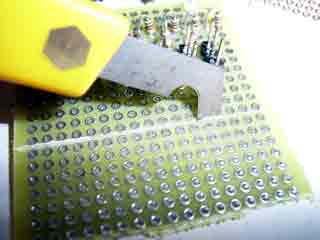

※秋月C基板を、Pカッターなどで横に切断するとちょうど良いサイズです。

ヘッダピンの3ピンと、DIP32の16ピンが合う位置にヘッダピンをマウントします。

※RESETやTRIGGERを使用する場合やサイズが気にならない方は、IDE等で使われている逆ざし防止機能つきの40ピンボックスヘッダもお勧めです。

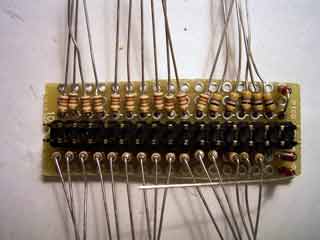

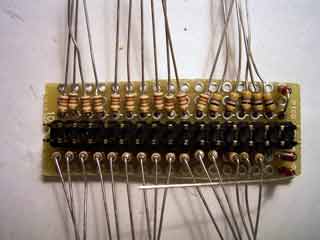

2.保護抵抗とツェナーダイオードを基板に取り付けて半田付けします。

抵抗の取り付け位置は、ケーブル用コネクタの干渉に注意します。

チップ抵抗を使うと見た目も綺麗ですっきりすると思います。私はオシロやロジアナのプローブでつまみたかったのでリードタイプで作りました。

※ツェナーダイオードとヘッダピンの配線も行います。(写真は配線前)

※VPPプログラム電圧保護が不要なら、ツェナーダイオードは省略できます。

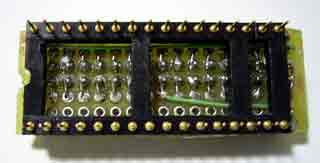

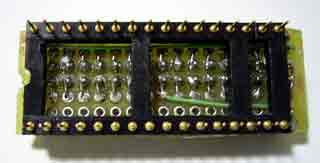

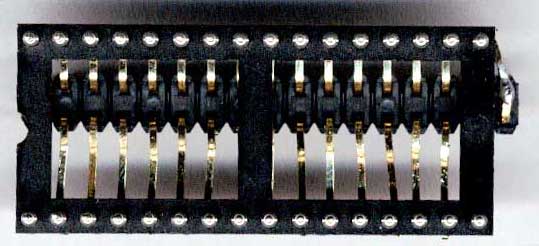

4.32ピンのピンソケットを基板に取り付け半田付けします。

※ここでは秋月電子通商のDIP40のピンを切断して使用しています。

※ICソケットを使用する場合、丸ピンではターゲットのICソケットを痛めることがあるので、平ピンの方が適しています。

5.完成です。IDE用40芯ケーブルでカメレオンUSBロジアナと接続します。

セットアップ

1.CPLDデザインファイルchamrome.jedをCPLDに書き込みます。

書き込みには、カメレオンUSBの使用方法に従い、cusbwr.exeを使います。

表だし(crome.jed)と裏だし(crome_r.jed)で、書き込みファイルが異なります。

2.chamrome.exeを適当なディレクトリにインストールします。

3.必要があれば、実行に便利なショートカットやバッチファイルを作成します。

使い方

1.カメレオンUSBロジアナをPCに接続します。

2.カメレオンUSBロジアナをROMエミュレータ用プローブ、ターゲットと接続します。

3.chamrome.exeをWindowsのコマンドプロンプトから実行して、データをダウンロードします。

形式:chamrome.exe {オプション...} [ファイル名]

[ファイル名]:転送するROMデータ、バイナリ形式

{オプション} -r[ROMタイプ] = ROMタイプ設定

2764,27128,27256,27512,27010,27020,27040,29040 から選択

-a = すべてのROMエリアを書き込む(省略時はファイル長にあわせる)

-p[PADコード] = PADコードを16進数で指定(省略時 0ffH)

-ts[アドレス] = シングルトリガ、アドレス設定

-tp[アドレス] = パルストリガ、アドレス設定

-tc[アドレス] = シングルトリガクリア

-s[on][off] = リセット制御、'L','H','Z'のいずれかで指定

-w = 終了時に'HIT ANY KEY'の表示とキー入力待ちをする

※必要に応じてショートカットを作成すると便利です。

・chamrome.exeをデスクトップに右ドラッグ&ドロップしてショートカットを作成。

・ショートカットのプロパティにあるリンク先にオプションを追加します。

例1:ダブルクリックで29EE020の固定ファイルをダウンロード/実行

リンク先:C:\tool\chamrome.exe -w -r27020 rom_data.bin

例2:ドラッグ&ドロップで27C256の任意のファイルをダウンロード/実行

リンク先:C:\tool\chamrome.exe -w -r27256 %1

※ROMデータのHEX-BIN変換等が必要な場合、バッチファイルである程度自動化ができます。

4.ターゲットの電源を入れる。

プローブの回路説明

基本的には32本のプローブ用信号にROMのピンを繋ぐだけですが、直結してしまうとCPLD(USB)の電源がOFFの時にプローブピンに電圧を印可すると、CPLDが壊れてしまうことがあります。

そこで、直列に抵抗を入れることで電流制限を行っています。

使用方法を絶対間違わなければ抵抗を省略できますが、面倒でも抵抗の挿入を強くお勧めします。

最初にういう直結タイプのプローブを作りましたが、案の定動作チェック中にCPLDが壊れました。

VPPになりうる端子にはプログラム時に+12.5V等が印可されるため、抵抗が入っていてもかなり危険です。そこでツェナーダイオードで端子電圧が5.1V以上にならないように保護しています。(ただしVPP=12Vを加えて良いわけではない)

ターゲットに書き込み機能がなければ、VPP保護は不要でしょう。

プローブとヘッダの方向が逆になっていますが、これはDPI32の16ピンをGNDに落とす必要があることと、DIP28の時にGNDピンを共有するためこの方向にしてあります。

ICソケットの16,17pin側にはみ出した部分をプローブ用コネクタの1ピン(GND)にあわせるようにします。これでDIP32の17ピンがPROBE0,16ピンがPROBE1と全ピンが順番につながります。※裏だしの場合

27C512以下のDIP28で使用する場合、DIP32の1,2,31,32ピンを余らせるようにして、DIP28ソケットを装着することで対応可能です。

作成したPROMプローブは、40芯のキーピンのないIDEケーブルでカメレオンUSBロジアナのプローブ用コネクタに接続します。※EIDE用80芯ケーブルも使えません

サポートROM

DIP28またはDIP32ピンで、よく使われている一般的な物に対応しています。

対応ROM一覧

| ROM名 | 形状 | 容量 | 説明 |

|---|

| 27C64 | DIP28 | 64KBit | 27C128からA13を削除したタイプ |

|---|

| 27C128 | DIP28 | 128KBit | 27C256からA14を削除したタイプ |

|---|

| 27C256 | DIP28 | 256KBit | 古くからごく一般的に使われているもの |

|---|

| 27C512 | DIP28 | 512KBit | 1pinがA15で、他が27C256と同じタイプ |

|---|

| 27C010/29F010 | DIP32 | 1MBit | 27C512をDIP32に延長した感じ,A16=2pin,(WE=31pin) |

|---|

| 27C020/29F020 | DIP32 | 2MBit | 27C010/29F010にA17を追加したもの、A17=30pin |

|---|

| 27C040 | DIP32 | 4MBit | 27C020にA18を追加したもの、A18=31pin |

|---|

| 29F040 | DIP28 | 4MBit | 29F020にA18を追加したもの、A18=1pin |

|---|

・PROM,FlashROMともに書き込み動作には未対応です。

特に27Cxxxシリーズや28Fxxxシリーズでは書き込み厳禁です。+12Vが印可されカメレオンUSBが壊れます

・FlashROMは、デバイスIDの読み込み等も未対応です。

・1Mbitはピン配置の違う物(マスクROMとコンパチ)がたまにあるので特に注意

・信号レベルは3.3V LVCMOレベルですが、5.0V TTLレベルにも適合します。

・ROMのVCC端子電圧がLレベルの時は、データ出力が禁止されます。

アクセスタイム、仕様

アドレス確定-データ出力:85nsec程度

CEアサート-データ出力:10ns程度

OEアサート-データ出力:10ns程度

アクセストリガー感度:20ns~40ns(50MHz x 2サンプリング)

トリガポイント位置遅延:40ns~60ns+α

トリガ最小パルス幅:20ns

CPLDの回路は100MHzでは動かなかったので、50MHzで駆動しています。

CPLDはMAX 100MHzですが、実際に100MHzで動かすようにデザインするのは困難なようです。信号の遅延時間がすぐに10nsを越えてしまいます。

100MHzでは動かなかった原因は、はっきりしませんが、100MHzでラッチする信号を絞っても絞ってもちゃんと動いてはくれませんでした。

ロジアナはよく100MHzで動いているなぁと感心してしまいます。

アドレス確定に対する最大アクセス時間は、アドレスSetupTime+サンプリングディレイ1クロック+メモリアクセス3クロック+出力遅延となります。

CEとOEに対するアクセス時間は3ステート制御の論理ゲートだけです。

アクセストリガーの検出は、2サンプルのコンペアを取っています。出力信号は、さらに1クロック後にラッチ出力されます。

CPLD側仕様

ターゲット(PROM)からのアクセスは非同期のランダムアクセスです。

回路の簡略化とアクセスタイム短縮のため、PBSRAMはパイプライン、非バーストリード動作を絶えず実行しています。

結構電流を食うようなので、USBパワーの貧弱な方は注意が必要かもしれません。

ホスト側からのアクセス時には、ターゲットエミュレーションを停止して、ホスト側に切り替えてから行います。

したがって、エミュレーション中にデータの書換えを行うことはできません。

ホストアクセスモードの時は、常時リード状態にあり、書き込みリクエストが発生すると、1ダブルワードを書き込んで、再びリード状態に戻ります。

ADV信号は、書き込みサイクルの時にHレベルにしなければならないようですが、ロジアナ基板ではLレベルに落ちていて制御できません。

そのせいかどうかはわかりませんが、現状では時々書き込み処理に失敗するため、リトライ処理を必要とします。

EZ-USBとのI/FはPC0~PC3をアドレスバスと考え、通常のメモリマップドI/Oと同様の方法で行います。

PC0~PC3で読み書きするレジスタを選択しておき、データエリアのアクセスで各レジスタをアクセスします。

書き込みレジスター(FWR=L)

| PC0~PC3 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 内容 |

|---|

| 00h | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | データ書き込み、注1、注2 |

| 01h | A7 | A6 | A5 | A4 | A3 | A2 | --- | --- | アドレスセット、注3、注4 |

| 02h | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | アドレスセット、注4 |

| 03h | --- | --- | --- | --- | --- | A18 | A17 | A16 | アドレスセット |

| 06h | EMU | RSE | RSL | TPM | --- | --- | --- | --- | モード設定 |

| 07h | --- | F18 | R18 | R17 | R16 | R15 | R14 | R13 | ROM選択、注5 |

注1:PBSRAMへの書き込み動作は、4バイト書き込み毎に行われる

注2:アドレスの下位12ビット(A0-A11)は読み書き毎に自動インクリメントされる。

注3:書き込み時、アドレス A0,A1は必ず0にする必要がある。

注4:データ書き込み時はプリインクリメントとなるため、下位12ビットのみ書き込むアドレスから4引いた値を設定する。

注5:R13~R18,F18でアドレスの有効/無効を設定することでROMを選択する

読み込みレジスター(FRD=L)

| PC0~PC3 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 内容 |

|---|

| 00h | RD7 | RD6 | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 | データリード |

| 04h | '0' | '0' | '0' | '0' | '0' | '0' | VCC | TRG | ステータス |

| 0dh | '0' | '1' | '0' | '1' | '0' | '0' | '1' | '0' | CPLDチェックコード'R' |

| 0eh | '0' | '1' | '0' | '0' | '0' | '1' | '0' | '1' | CPLDチェックコード'E' |

| 0fh | '0' | '0' | '0' | '1' | '0' | '0' | '0' | '0' | Version 10h |

EZ-USB側ファーム仕様

カメレオンUSBの汎用ファーム(gpfw.c)を使用しています。

ただし、バーストリード処理にバグがあったため、バグ修正版を使用しています。

気をつけた点は、CPLD側のデータ書き込みシーケンスをFWRITE連続書き込み対応にしたことです。

4096バイト単位でFWRITE書き込みが可能なため、転送時間は4Mbitで2秒弱(書き込みのみ)と非常に高速です。

ファームウェアはchamrome.exeに組み込まれているので、chamrome使用時には気を遣う必要はありません。

ソフトウェアの仕様

特に難しいことはしていません。

汎用ファームとCPLDの決まり事に従ってバルク転送をおこなうだけです。

CPLDが別のデザインでプログラムされているときにPC0~PC3が出力同士でぶつかるのを避けるために、いちばん最初にCPLDのチェックコードを調べています。

ポートPCとCPLDの間にも、直列抵抗が欲しいところです。

動作確認

・FPGA-PACMAN (27020)

・Xeltek SUPERPRO/LX (Universal Writer)

SST 29EE2020 (27020)

HITACHI 27C256H (27256)

※ユニバーサル/ROMライタによる動作確認は、危険なのでお勧めはできません。

・秋月H8ボード(シーエー様にてデバッグ)

裏だし

裏だし