2007.11.5 怴婯

DCO偲偼丠

丂DCO(DigitalControledOscrator)偼僨僕僞儖怣崋偱廃攇悢傪惂屼偱偒傞敪怳婍偺帠傪巜偟傑偡丅

丂崱夞偼FPGA偺儘僕僢僋偱敪怳婍傪嶌偭偰偟傑偊偲偄偆柍杁側幚尡偱偡丅

丂廃攇悢僔儞僙僒僀僓(FrequencySynthesizer)偲偄偊偽丄恀偭愭偵PLL(PhaseLockedLoop)傪巚偄偮偔偺偱偼側偄偱偟傚偆偐丅

丂PLL偼僋儘僢僋偺埵憡嵎傪専弌偡傞偙偲偱僋儘僢僋偵傕偆堦曽偺僋儘僢僋傪摨挷偝偣傞惂屼憰抲傪巜偟傑偡偑丄堦斒揑偵偼廃攇悢僔儞僙僒僀僓偦偺傕偺傗VCO亄暘廃婍亄PLL傪傑偲傔偰PLL偲屇傇帠偑懡偄傛偆偱偡丅

丂偙傟偼傎偲傫偳偺PLL幃廃攇悢僔儞僙僒僀僓偑丄儕僼傽儗儞僗僋儘僢僋丄VCO丄暘廃婍丄PLL丄儖乕僾僼傿儖僞偱峔惉偝傟丄偦偺偆偪偺PLL丄暘廃婍丄VCO(VoltageControledOscrator)偺俁偮傪儌僕儏乕儖壔偟偰丄儕僼傽儗儞僗僋儘僢僋偲儖乕僾僼傿儖僞傪奜晹僐儞億乕僱儞僩偲偟偰愙懕偡傞偙偲偑懡偄堊偱偟傚偆丅

丂偟偐偟丄偙偙偱偼PLL偼弮悎偵惂屼憰抲偲偟偰埖偆偺偱PLL偵暘廃婍傗敪怳婍偑娷傑傟側偄偙偲傪擮摢偵抲偄偰偔偩偝偄丅偦偟偰敪怳婍偼VCO偱偼側偔DCO傪巊偄傑偡丅

儘僕僢僋偩偗偱敪怳偡傞丠

丂斀揮儘僕僢僋偵俠俼偺帪掕悢偲僸僗僥儕僔僗傪帩偨偣偨偄傢備傞俠俼敪怳偱偼側偔丄弮悎側儘僕僢僋偩偗偱傕敪怳婍傪嶌傟傑偡丅

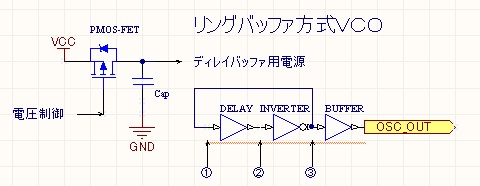

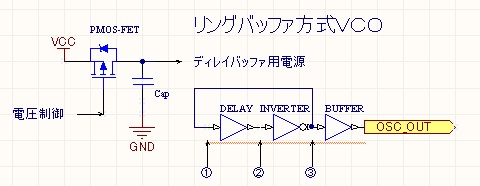

丂偙傟偼儕儞僌僶僢僼傽幃偺敪怳婍摍偲屇偽傟傞傛偆偱偡丅傑偢偼儕儞僌僶僢僼傽幃偺倁俠俷偺夞楬偺尨棟傪峫偊傑偡丅

丂夞楬偺摦嶌傪捛偄偐偗傑偡丅

丂僎乕僩夞楬偵偼擖椡偐傜弌椡傊怣崋揱払偵堦掕偺抶墑傪帩偪丄揱払偡傞偲偒偵堦掕帪娫偩偗抶傟傑偡丅

丂傑偨丄抶墑帪娫偼揹尮揹埑偵斀斾椺偟偰憹尭偟傑偡丅

丂僎乕僩娫抶墑偼偲傝偁偊偢1ns偲壖掕偟偰傒傑偡丅

丂嘆偺抧揰偑'L'偩偲偡傞偲丄1ns屻偵嘇偑'L'偵側傝丄偝傜偵1ns屻偵偼嘊偑斀揮弌椡偱'H'偵側傝傑偡丅

丂嘊偲嘆偼宷偑偭偰偄傞偺偱丄嘆偑'L'偵側偭偰偐傜2ns屻偵'H'偵側傞偙偲偵側傝傑偡丅

丂嘆偑'H'偵側傞偲丄偦偺2ns偵嘊偑'L'偵側傝丄嘆傕傑偨'L'偵栠偭偰偄傑偡丅

丂偙偺摦嶌傪4ns枅偵孞傝曉偡偺偱丄4ns廃婜亖250MHz偱敪怳偟偰偄傞偙偲偵側傝傑偡丅

丂偙偙偱揹尮揹埑偑壓偑傝丄僎乕僩娫抶墑偑2ns偵憹壛偡傞偲偳偆側傞偱偟傚偆偐丅

丂廃婜傕扨弮偵俀攞偺8ns偲側傝125MHz偱敪怳偲偄偆偙偲偵側傝傑偡丅揹尮揹埑偺憹尭偱廃攇悢偑惂屼偱偒偰偄傑偡丅

丂幚嵺偵丄偙傫側偵偆傑偔摦嶌偡傞偱偟傚偆偐丠

丂摎偊偼Yes偱偡丅74HC04摍偺斈梡僀儞僶乕僞俁抜偺儖乕僾偱傕100MHz慜屻偱敪怳偱偒傑偡偟丄50MHz乣150MHz掱搙偺愱梡VCO僠僢僾傕懚嵼偟傑偡丅

丂偨偩偟丄揹尮揹埑偺曄壔傗僺儞偺婑惗梕検丄屄懱嵎偵傛傞廃攇悢曄摦偑僔價傾側偺偱丄揹埑抣偵懳偡傞廃攇悢偺愨懳惛搙偼摼傜傟傑偣傫丅廃攇悢偺埨掕搙傕僋儕僗僞儖傗僙儔儘僢僋側偳偵媦傃傑偣傫丅偦偙偱VCO傪巜掕偟偨廃攇悢偵曐偮偨傔偵PLL摍偑巊梡偝傟傑偡丅

丂娙棯壔偺堊偵僨傿儗僀儔僀儞偼俀抜偲偟傑偟偨偑丄幚嵺偵偼俀抜偲偼尷傝傑偣傫丅

丂傑偨丄幚嵺偺夞楬偱偼揹尮埨掕壔偺偨傔偺LC僼傿儖僞摍傕昁梫偱偡丅

丂偝偰丄師偑杮戣偺儕儞僌僶僢僼傽幃DCO偱偡丅

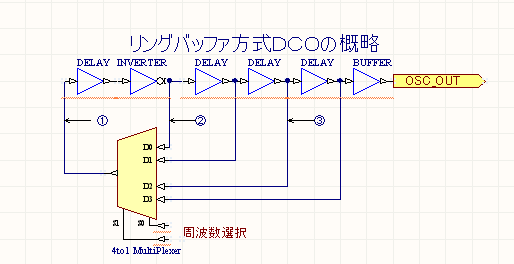

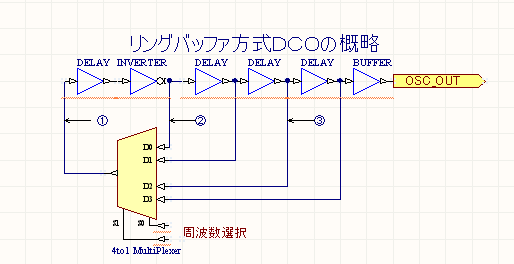

丂僎乕僩偺抶墑偲斀揮儖乕僾偵傛傞敪怳曽朄偼儕儞僌僶僢僼傽幃VCO偲摨偠偱偡偑丄抜悢偑憹偊偰丄僨乕僞僙儗僋僞偑捛壛偝傟偰偄傑偡丅

丂偙偙偱傕僎乕僩娫抶墑傪1ns偲壖掕偟偰傒傑偡丅乮曋媂忋僙儗僋僞偺抶墑偼侽傪夁掱偟傑偡丅乯

丂僙儗僋僞偱侽傪慖傇偲嘇偐傜偺儖乕僾僶僢僋偱抜悢偼俀抜丄2ns x 2 = 4ns(250MHz)偱偡丅

丂僙儗僋僞偱俀傪慖傇偲嘊偐傜偺儖乕僾僶僢僋偱抜悢偼係抜丄5ns x 2 =10ns(125MHz)偱偡丅

丂僨僕僞儖怣崋偺慖戰偱廃攇悢偑曄壔偟傑偡丅

丂娙棯壔偺堊偵忋婰偱偼慖戰巿傪係庬椶偲偟傑偟偨偑丄幚嵺偼慖戰悢傪俉乣俁俀掱搙偵偟傑偡丅

VCO vs DCO

丂DCO偼揹埑偲偄偆傾僫儘僌梫慺傪帩偨側偄偨傔儖乕僾僼傿儖僞偺傛偆側奜晹僐儞億乕僱儞僩偑晄梫偱偡丅

丂偟偐偟丄廃攇悢偺暘夝擻偑棟榑忋柍尷偺VCO偵懳偟偰DCO偼侾抜偺僨傿儗僀扨埵枹枮偺挷惍偑弌棃傑偣傫丅

丂傑偨丄DCO偺曽偑儖乕僾抜悢傪懡偔昁梫側偨傔丄嵟戝廃攇悢傕掅偔側傝傑偡丅

丂尵偄姺偊傞偲DCO偼愝寁傗惂屼偼娙扨偩偑丄廃攇悢惈擻傗惛搙乮僕僢僞乯偑埆偄偲偄偆偙偲偱偡丅

丂偟偐偟僕僢僞偵栚傪偮傇偭偰偟傑偊偽丄PLL摍偱VCO偲摨條偵DCO傕惓妋側廃攇悢傪崗傓偙偲偑偱偒傞偼偢偱偡丅

丂幚嵺偺惢昳偲偟偰偼丄Ti幮偺MSP430僔儕乕僘偑撪晹敪怳婍偲偟偰DCO傪嵦梡偟偰偄傑偡丅僼傿乕僪僶僢僋夞楬偼PLL偱偼側偔FLL(FrequencyLockedLoop)偲偄偆曽朄偩偦偆偱偡丅

丂DCO偦偺傕偺偱偼偁傝傑偣傫偑丄Xilinx FPGA偺DLL(DelayLockedLoop)傗DFS(DigitalFrequencySynthesizer)傕DCO偲椶帡偟偨夞楬偱偡丅

丂FPGA愱梡偺DCM傪巊偭偰嫵壢彂捠傝偵DFS傪峔抸偟偰傕慡偔柺敀偔偁傝傑偣傫丅FPGA偺撪晹儘僕僢僋傪僾儘僌儔儉偟偰奜晹僐儞億乕僱儞僩柍偟偱敪怳偡傞DCO偲惂屼夞楬傪慻傒崌傢偣偰DFS傪嶌傝傑偡丅

丂傑偢偼DCO偱敪怳偝偣傞偙偲偱偡丅偙傟偑弌棃側偗傟偽愭偵恑傒傑偣傫丅

FPGA偱DCO

丂偙偙偐傜偼丄偁偔傑偱傕幚尡側慬抲偱偁傝丄幚梡惈偼奆柍偱偁傞偙偲傪慜婰偟偰偍偒傑偡丅

丂FPGA偼旕摨婜怣崋傪儖乕僾偝偣傞傛偆側巊偄曽偼憐掕偝傟偰偍傜偢丄杮棃偙偺傛偆側巊偄曽傪偟偰偼偄偗傑偣傫丅

丂偙偙偱偼偁偔傑偱傕幚尡憰抲偲偟偰FPGA傪巊偆偺偩偲峫偊偰偔偩偝偄丅

丂FPGA偺榑棟夞楬晹暘偺婎慴扨埵偼丄戝掞係擖椡侾弌椡偺LUT偱偡丅係偮偺擖椡偵懳偟偰弌椡偺抣偑擟堄偵曄壔偡傞彫偝側旕摨婜ROM偲峫偊傜傟傑偡丅

丂LUT偵偼FF(僼儕僢僾僼儘僢僾)偑僙僢僩偵側偭偰偄偰捠忢偼悢抜偺LUT傪捠偟偨傜FF偱儔僢僠偝偣偰摨婜夞楬傪峔惉偟傑偡丅偟偐偟崱夞偼FF傪巊傢偢偵LUT偩偗傪巊偄傑偡丅

丂LUT傕榑棟夞楬側偺偱揱払抶墑傪帩偭偰偄傑偡丅LUT亖僨傿儗僀偲峫偊傟偽丄巜掕抜悢偺儕儞僌僶僢僼傽僆僔儗乕僞傪嶌傟偦偆偱偡丅

丂偙偺婰帠傪幏昅拞丄偨傑偨傑尒偨Xilinx偺傾僾儕働乕僔儑儞僲乕僩偵摨偠峔惉偺僨傿儗僀夞楬偑尒偮偐偭偨丅DCO偲偟偰偺巊梡偼偳偆偩偐暘偐傜側偄偑丄LUT傪婜懸偝傟偨僨傿儗僀儔僀儞偲偟偰巊偆帠偼偁側偑偪娫堘偭偨峫偊曽偱偼側偄傜偟偄

丂偝偰丄FPGA偵幚憰偡傞偵偁偨偭偰偼偄偔偮偐栤戣偑偄偔偮偐偁傝傑偡丅弴斣偵夝寛偟偰偄偄偒傑偡丅

丂傑偢嵟弶偵丄FPGA偼懡擖椡僨乕僞僙儗僋僞偑嬯庤偲偄偆偙偲偱偡丅

丂忋恾偺夞楬峔惉偱偼僨乕僞僙儗僋僞偼僨傿儗僀儖乕僾偺堦娐偱偁傝丄堦掕偺僨傿儗僀傪帩偮偙偲偑昁梫偱偡偑懡擖椡偺僨乕僞僙儗僋僞偺応崌丄FPGA偱偼懡抜壔偝傟偨MUX傗LUT偱峔惉偝傟偰偟傑偄丄愝掕抣偛偲偵堦掕偺僨傿儗僀傪帩偮偙偲傪婜懸偱偒傑偣傫丅

丂傑偨丄擖椡怣崋偺偳傟偐堦偮偼忢偵昁偢曄壔偟偰偄傞忬懺偱丄僌儕僢僕僲僀僘摍偺梫場偱惓忢摦嶌偟側偄偐傕偟傟傑偣傫丅

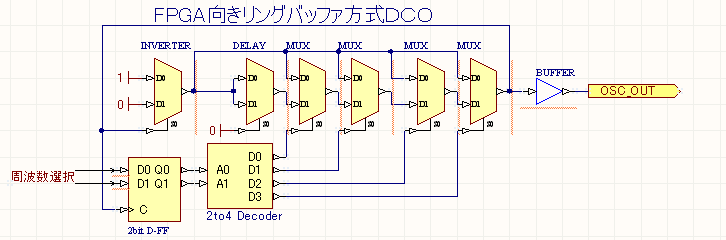

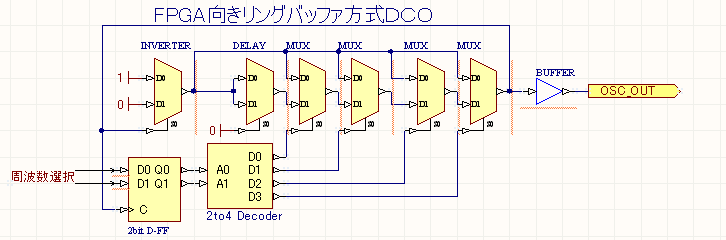

丂偦偙偱丄FPGA偵揔偟偨峔惉偱夞楬傪峔抸偟傑偡丅

丂偙偺夞楬偱偼丄奺僨傿儗僀傪儅儖僠僾儗僋僒偱峔惉偟偰丄偦傟傜傪屄暿偺僗僀僢僠偱愗傝懼偊偰偄傑偡丅

丂奺僨傿儗僀偼慜抜僨傿儗僀弌椡偲丄僶僀僷僗擖椡偺偳偪傜偐傪擖椡偡傞偙偲偑弌棃傑偡丅嵟廔抜傪僶僀僷僗擖椡偵偡傞偲嵟抁儖乕僾丄偡傋偰傪僨傿儗僀弌椡偵宷偖偲嵟挿儖乕僾偲側傝丄愝掕抣偱僨傿儗僀抜悢傪曄峏偱偒傑偡丅

丂偮偄偱偵僀儞僶乕僞乕傕MUX偱峔惉偟偰偟傑偄傑偡丅偙傟側傜俁擖椡侾弌椡偺LUT偺侾庬椶偝偊埨掕偱偒傟偽丄抜悢偑偄偔偮憹偊偰傕僋儕僥傿僇儖側儖乕僾撪傪埨掕壔偱偒傑偡丅

丂師偵慖戰怣崋偺峏怴僞僀儈儞僌偱偡丅

丂怣崋曄壔拞偵僨傿儗僀儔僀儞傪愗傝懼偊偰偟傑偆偲晄惓敪怳傪惗傒弌偟傑偡丅

丂偦偙偱僗僀僢僠傪帩偨側偄屌掕僨傿儗僀傪悢抜捠偟偰丄怣崋曄壔偑屌掕儔僀儞傪捠夁拞偵僗僀僢僠偺愗傝懼偊傪峴偆傛偆偵偟傑偡丅

丂屌掕僨傿儗僀捠夁拞偱偁偭偰傕丄慖戰怣崋偺曄壔偱壜曄僨傿儗僀撪偺怣崋偑曄壔偡傞偲晄惓敪怳傪惗傒弌偟傑偡丅僶僀僷僗偝傟偰偄傞枹巊梡僨傿儗僀儔僀儞偼丄慡偰僶僀僷僗懁傊僗僀僢僠偟偰偍偒傑偡丅

丂崱夞偺幚尡偱偼徣棯偟傑偟偨偑丄僨傿儗僀儔僀儞偼婲摦帪偵儕僙僢僩傪峴偭偨傎偆偑埨慡偱偡丅奜棃僲僀僘摍偱僨傿儗僀儔僀儞偑晄埨掕側忬懺偵側傞偲丄晄埨掕側忬懺傪塱墦偵儖乕僾偡傞偙偲偵側傝傑偡丅

弶抜僀儞僶乕僞乕偺擖椡怣崋偺偳偪傜偐侾偮傪斀揮偝偣傞偲丄僨傿儗僀儔僀儞偺怣崋偑侽偐侾偵屌掕偝弶婜壔偝傟傑偡丅

丂嵟屻偺戝偒側栤戣偼丄榑棟崌惉僣乕儖偺帺摦嵟揔壔偱偡丅

丂FPGA偼摨婜夞楬傪慜採偲偟偰偄傞偺偱丄榑棟崌惉僣乕儖偼抶墑偑彮偝偔夞楬偑彫偝偔側傞傛偆偵儘僕僢僋偺嵟揔壔傪峴偄傑偡丅

丂奺抜偺僨傿儗僀儔僀儞偼榑棟揑偵摨堄側偺偱丄偙偺嵟揔壔偵傛偭偰堦晹偑徚柵偟偰偟傑偆偙偲偑偁傝傑偡丅

丂Xilinx WebPack 7.1i偱偼LUT3傗ROM16S偺愱梡僾儕儈僥傿僽偱婰弎偟偨応崌丄嶰抜偺僨傿儗僀儔僀儞傪侾偮偺LUT偵揨傔傜傟偰偟傑偄傑偟偨丅

丂嵟揔壔偺僆僾僔儑儞愝掕傪扵偟傑偟偨偑丄梷惂弌棃偨偺偼僔儞僙僒僀僘帪偺嵟揔壔偩偗偱丄僀儞僾儕儊儞僩帪偺嵟揔壔傪梷惂偡傞僗僀僢僠偼尒偮偐傝傑偣傫偱偟偨丅

丂偦偙偱丄僾儕儈僥傿僽偵RAM16X1S傪巊梡偟傑偟偨丅LUT偺儘僕僢僋偑彂偒姺傢傞壜擻惈偑偁傟偽偦偙偼嵟揔壔偟傛偆偑偁傝傑偣傫丅RAM32S偵擟堄偺弶婜抣傪杽傔崬傫偱偍偗偽儅儖僠僾儗僋僒偲偟偰婡擻偟傑偡丅

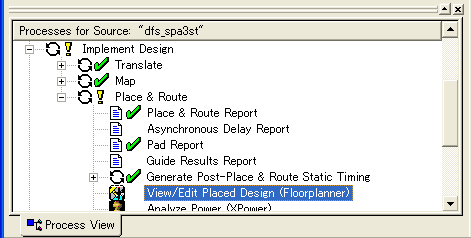

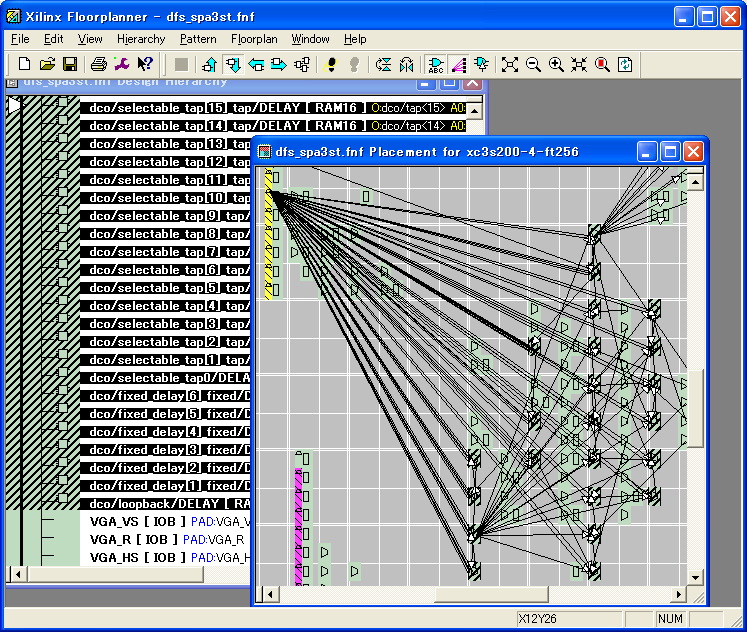

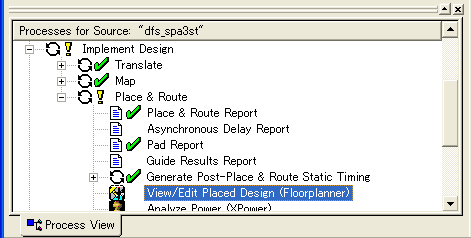

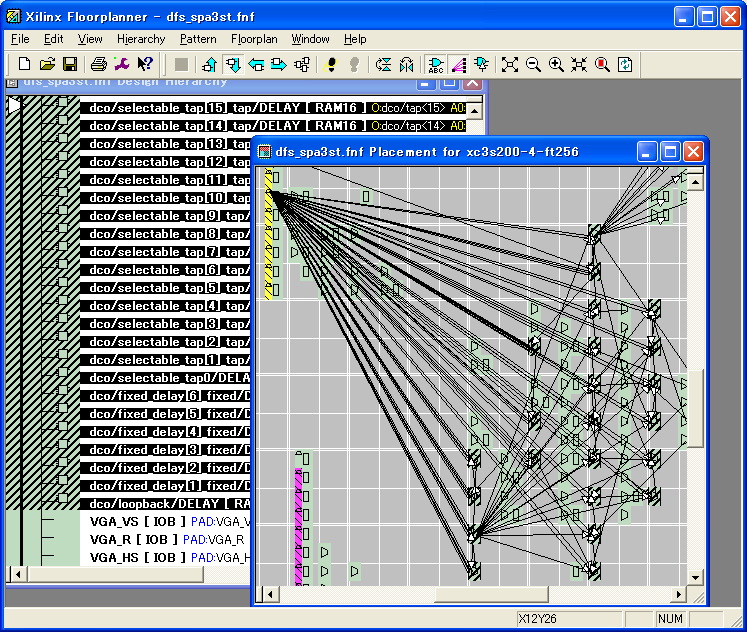

丂昡壙僨僓僀儞偱偼彂偒崬傒僋儘僢僋傪侽偵屌掕偟偰偄傑偡丅ISE偺僶乕僕儑儞偵傛偭偰偼嵟揔壔偺懳徾偵側傞偐傕偟傟傑偣傫偺偱丄僨傿儗僀儔僀儞偑暔棟攝抲偝傟偨偐偳偆偐偼昁偢妋擣偟傑偡丅Xilinx ISE側傜

丂偐傜Floorplanner傪婲摦偟偰丄僨傿儗僀儔僀儞偺僾儕儈僥傿僽傪慖戰偟傑偡丅

丂崱夞偺僨傿儗僀儔僀儞偼屌掕俉抜亄壜曄侾俆抜乮侾俇抜奒乯偺愝寁偱偡丅夋柺塃懁偑FPGA偺撪晹攝抲恾偱幚嵺偵俀俁屄偺LUT偑妱傝摉偰傜傟偰偄傞偙偲偑妋擣偱偒傑偡丅

丂埲壓丄FPGA偱僼傿乕僪僶僢僋惂屼壜擻側DCO傪峔惉偡傞偨傔偺梫審偱偡丅

丒奺僨傿儗僀儔僀儞偼暔棟揑偵LUT偵攝抲偟偰丄偦傟偧傟偑堦掕偺抶墑帪娫傪帩偮偙偲

丒僨傿儗僀儔僀儞娫偺攝慄抶墑偼丄僨傿儗僀儔僀儞偦偺傕偺偺抶墑帪娫傛傝廫暘彫偝偄偙偲

丒僨傿儗僀儔僀儞偺俀偮偺MUX偺擖椡偵懳偡傞弌椡抶墑偺嵎偑丄攝慄抶墑傛傝廫暘彫偝偄偙偲

丒廃攇悢偺崅掅偑丄愝掕抣偺弴斣捠傝偵弴彉傛偔曄壔偡傞偙偲

丒敪怳廃攇悢偺僕僢僞乮備傜偓乯偵傛偭偰丄椬愙偡傞愝掕抣偺廃攇悢傪挻偊側偄偙偲

DCO偺幚尡

丂偝偰丄婘忋偺嬻榑偼偙偺傊傫偵偟偰偍偄偰幚婡偵傛傞幚尡傪偟傑偡丅

丂偙偆偄偭偨偨偖偄偺幚尡偼愝寁抣傗僔儈儏儗乕僞乕偺寢壥偱偼梊應偱偒傑偣傫丅

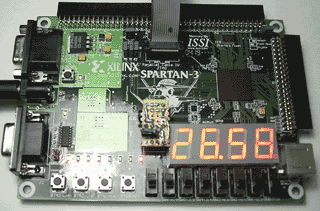

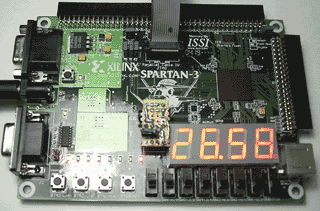

丂幚尡偵偼Spartan3StarterKit傪巊偄傑偟偨丅偙偙偐傜僨僓僀儞傪僟僂儞儘乕僪偱偒傞偺偱僉僢僩傪偍帩偪偺曽偼幚嵺偵帋偟偰傒傞偙偲偑弌棃傑偡丅

丂偙偺僨僓僀儞偵偼丄PLL偵傛傞僼傿乕僪僶僢僋惂屼夞楬傕婛偵娷傑傟偰偄傑偡丅徻偟偄愢柧偼僜乕僗撪偺僐儊儞僩傪嶲徠偟偰偔偩偝偄丅

Spartan3StarterKit偺僗僀僢僠傪慡偰OFF偵偟偰揹尮傪擖傟丄幚尡僨僓僀儞傪僐儞僼傿僌儗乕僔儑儞偟傑偡丅

偙偺忬懺偱丄俈僙僌儊儞僩俴俤俢偵偼柍埨掕偺DCO敪怳廃攇悢偑MHz扨埵偱昞帵偝傟傞傛偆偵偟偰偁傝傑偡丅

丂偲傝偁偊偢摦偄偰偄傞條巕偱偡丅奜晹僋儘僢僋傪巊傢偢偵丄Spartan3撪晹偐傜26.58MHz偺僋儘僢僋偑敪惗偟偰偄傑偡丅

丂師偼丄偙偺DCO偺摿惈傪幚應偟偰丄僼傿乕僪僶僢僋惂屼壜擻偐偳偆偐傪専徹偟傑偡丅

亅亅亅尰嵼丄婰帠偼偙偙偱廔椆偟偰偄傑偡丅亅亅亅

偛堄尒丄偛姶憐偑偁傝傑偟傜傜偙偪傜偺宖帵斅傊偍婅偄偟傑偡丅斀嬁偑懡偗傟偽懕偒傪媫偓傑偡丅